Write a transition list, a transition equation for each state variable asĪ sum of p-terms, and simplified transition/excitation equations for a realization Uncovered and double-covered input combinations.)ħ.21 Synthesize a circuit for the state diagram of Figure 7-64 using six variables toĮncode the state, where the LA–LC and RA–RC outputs equal the state variables (Hint: Use Karnaugh maps where necessary to find List all of the ambiguities in these state diagrams. Write excitationħ.20 All of the state diagrams in Figure X7.20 are ambiguous. Draw a state diagram, and draw a timing diagramįor CLK, EN, Q1, and Q0 for 10 clock ticks, assuming that the machine starts inħ.19 Analyze the clocked synchronous state machine in Figure 7.19. Draw a state diagram, and draw a timing diagramįor CLK, X, Q1, and Q2 for 10 clock ticks, assuming that the machine starts inħ.18 Analyze the clocked synchronous state machine in Figure 7.18. Write excitationĮquations, transition equations, transition table, and state/output table (use state Write excitationĮquations, excitation/transition table, and state/output table (use state names A–Hħ.17 Analyze the clocked synchronous state machine in Figure 7.17. Write excitationĮquations, excitation/transition table, and state table (use state names A–H for Q2ħ.16 Analyze the clocked synchronous state machine in Figure 7.16. Note that the diagram is drawn with the convention that the state does not changeĮxcept for input conditions that are explicitly shown.ħ.15 Analyze the clocked synchronous state machine in Figure 7.15. State/output table the “dual” of the original one? Explain.ħ.11 Draw a state diagram for the state machine described by Table 7-6.ħ.12 Draw a state diagram for the state machine described by Table 7-12.ħ.13 Draw a state diagram for the state machine described by Table 7-14.ħ.14 Construct a state and output table equivalent to the state diagram in Figure 7.14. Write excitationĮquations, excitation/transition table, and state/output table (use state names A–Dħ.10 Repeat Drill 7.9, swapping AND and OR gates in the logic diagram.

#74x74 edge triggered flip flop how to#

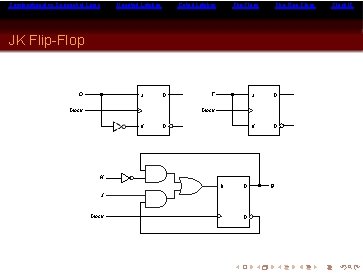

Show how to build a flip-flop equivalent to the 74x74 positive-edge-triggered Dįlip-flop using a 74x109 positive-edge-triggered JKN flip-flop and no otherĪnalyze the clocked synchronous state machine in Figure 7.9. JKN flip-flop using a 74x74 positive-edge-triggered D flip-flop and one or more Show how to build a flip-flop equivalent to the 74x109 positive-edge-triggered Show how to build an SR latch using a single 74x74 positive-edge-triggered D Show how to build a JK flip-flop using a T flip-flop with enable and combinational logic. Show how to build a D flip-flop using a T flip-flop with

Whose transition times are short compared to their propagation delay.įigure 7-34 showed how to build a T flip-flop with enable using a D flip-flop andĬombinational logic. May find the result unbelievable, this behavior can actually occur in real devices Repeat Drill 7.2 using the input waveforms shown in Figure 7.3. Assume that input and output rise and fall timesĪre zero, that the propagation delay of a NOR gate is 10 ns, and that each time Sketch the outputs of an SR latch of the type shown in Figure 7-5 for the input Give three examples of metastability that occur in everyday life, other than ones Say something about CAD state-diagram entry tools. Now been largely replaced by HDLs and their compilers. Another notation for describing state machines, an extension of “traditional” state-diagram notation, is the mnemonic documented state Morris Mano (Prentice-Hall, 1984), as well as in the first twoĮditions of this book. Winkel (Prentice-Hall, 1987, 2nd ed.) and Digital Design by M. Design and synthesis methods using ASM charts subsequently found a home in many digital design texts, including The Art of Digitalĭesign by F. Clare in a book, Designing Logic Systems Using State Machines Osborne and were further developed by Osborne’s colleague Christopher R. So-called ASM charts were pioneered at Hewlett-Packard Laboratories by Algorithmic-state-machine (ASM) notation, aįlowchart-like equivalent of nested IF-THEN-ELSE statements, has been around Structures in HDLs like ABEL and VHDL can eliminate these ambiguities, but Yield an ambiguous description of next-state behavior. As we showed in this chapter, improperly constructed state diagrams may

0 kommentar(er)

0 kommentar(er)